Tính năng, đặc điểm

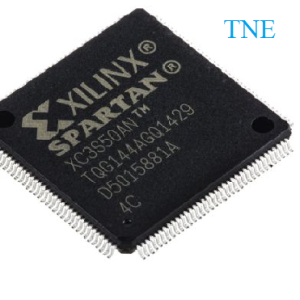

• Gia đình Spartan-6:

• Spartan-6 LX FPGA: Tối ưu hóa logic

• Spartan-6 LXT FPGA: Kết nối nối tiếp tốc độ cao

• Được thiết kế cho chi phí thấp

• Nhiều khối tích hợp hiệu quả

• Tối ưu hóa lựa chọn các tiêu chuẩn I / O

• Miếng đệm so le

• Gói nhựa ngoại quan khối lượng lớn

• Công suất tĩnh và động thấp

• Quá trình 45nm được tối ưu hóa cho chi phí và năng lượng thấp

• Chế độ giảm nguồn ngủ đông cho nguồn điện bằng không

• Chế độ treo duy trì trạng thái và cấu hình với

đánh thức nhiều pin, tăng cường kiểm soát

• Điện áp lõi 1.0V công suất thấp hơn (chỉ có LX, chỉ -1L)

• Điện áp lõi 1,2V hiệu suất cao (LX và LXT

Các loại tốc độ đồ họa, tốc độ -2, -3 và -3N)

• Ngân hàng giao diện SelectIO ™ đa điện áp, đa tiêu chuẩn

• Tốc độ truyền dữ liệu lên tới 1.080 Mb / giây cho mỗi I / O khác biệt

• Ổ đĩa đầu ra có thể lựa chọn, tối đa 24 mA mỗi pin

• Các tiêu chuẩn và giao thức 3,3V đến 1,2VI / O

• Giao diện bộ nhớ HSTL và SSTL chi phí thấp

• Tuân thủ trao đổi nóng

• Tốc độ xoay I / O có thể điều chỉnh để cải thiện tính toàn vẹn tín hiệu

• Bộ thu phát nối tiếp GTP tốc độ cao trong các LXT

• Lên tới 3,2 Gb / s

• Giao diện tốc độ cao bao gồm: ATA nối tiếp, Aurora,

Ethernet 1G, PCI Express, OBSAI, CPRI, EPON,

GPON, DisplayPort và XAUI

• Khối điểm cuối tích hợp cho thiết kế PCI Express (LXT)

• Hỗ trợ công nghệ PCI® chi phí thấp tương thích với

Thông số kỹ thuật 33 MHz, 32 và 64 bit.

• Các lát DSP48A1 hiệu quả

• Xử lý tín hiệu và số học hiệu suất cao

• Số nhân 18 x 18 và bộ tích lũy 48 bit nhanh

• Khả năng đường ống và xếp tầng

• Trình bổ sung trước để hỗ trợ các ứng dụng bộ lọc

• Khối điều khiển bộ nhớ tích hợp

• Hỗ trợ DDR, DDR2, DDR3 và LPDDR

• Tốc độ dữ liệu lên tới 800 Mb / giây (băng thông tối đa 12,8 Gb / giây)

• Cấu trúc xe buýt nhiều cổng với FIFO độc lập để giảm

vấn đề thời gian thiết kế

• Tài nguyên logic dồi dào với khả năng logic tăng

• Đăng ký thay đổi tùy chọn hoặc hỗ trợ RAM phân tán

• LUT 6 đầu vào hiệu quả cải thiện hiệu suất và

giảm thiểu sức mạnh

• LUT với flip-flop kép cho các ứng dụng trung tâm đường ống

• Chặn RAM với nhiều mức độ chi tiết

• RAM khối nhanh với tính năng ghi byte

• Khối 18 Kb có thể được lập trình tùy ý thành hai

RAM khối 9 Kb độc lập

• Ngói quản lý đồng hồ (CMT) để nâng cao hiệu suất

• Tiếng ồn thấp, xung nhịp linh hoạt

• Trình quản lý đồng hồ kỹ thuật số (DCM) loại bỏ độ lệch của đồng hồ

và biến dạng chu kỳ nhiệm vụ

• Vòng lặp khóa pha (PLL) cho xung nhịp thấp

• Tổng hợp tần số với phép nhân đồng thời,

phân chia và dịch pha

• Mười sáu mạng đồng hồ toàn cầu có độ lệch thấp

• Cấu hình đơn giản, hỗ trợ các tiêu chuẩn chi phí thấp

• Cấu hình tự động phát hiện 2 pin

• SPI của bên thứ ba rộng (tối đa x4) và hỗ trợ flash NOR

• Tính năng Flash Nền tảng Xilinx phong phú với JTAG

• Hỗ trợ MultiBoot để nâng cấp từ xa với nhiều

dòng bit, sử dụng bảo vệ watchdog

• Tăng cường bảo mật để bảo vệ thiết kế

• Định danh DNA thiết bị duy nhất để xác thực thiết kế

• Mã hóa dòng bit AES trong các thiết bị lớn hơn

• Xử lý nhúng nhanh hơn với chi phí thấp, nâng cao,

Đánh giá

Chưa có đánh giá nào.